| PC-6001 僄儈儏儗乕僞奐敪擔婰 |

| 仭 [08/08/09] - WAIT怣崋 |

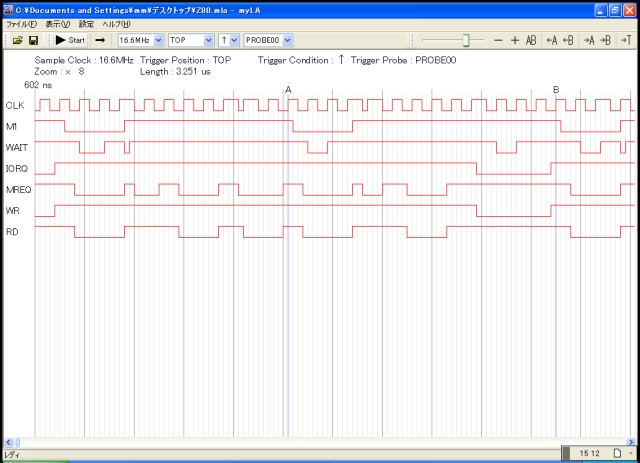

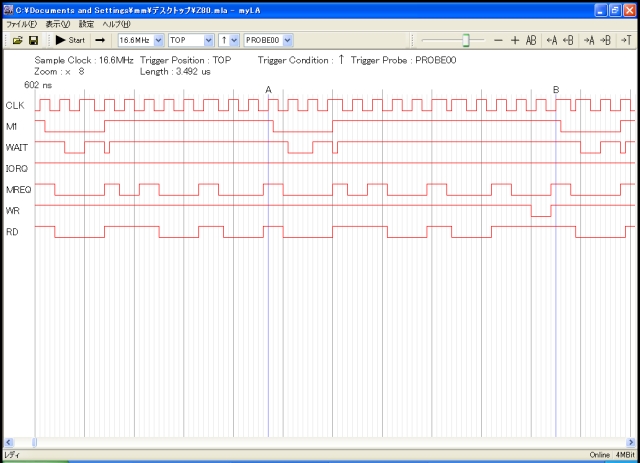

PC-6001弶戙偺WAIT怣崋偵偮偄偰婰榐丅

ORG 0DF00H DI LD A,02H OUT (93H),A LP: OUT (0A0H),A JP LP

EXEC &HDF00偟偰丄OUT柦椷偲JP柦椷偑岎屳偵幚峴偝傟偰偄傞條巕傪儘僕傾僫偱妋擣偟傑偟偨丅

惵偄慄偺儅乕僇乕儔僀儞A-B偺嬫娫偑OUT柦椷偺幚峴忬懺偱偡丅嵟弶偺柦椷僼僃僢僠偱M1怣崋偑Active偵側傝傑偡偑丄 偦偺僞僀儈儞僌偱WAIT偑1Clock暘偩偗擖傝傑偡丅偙傟偼埲慜偐傜傢偐偭偰偄偨偺偱偡偑丄IORQ偺僞僀儈儞僌偱傕 WAIT怣崋偑Active偵側傝傑偡丅偮傑傝丄OUT柦椷偱偼+2Clock偲側傝傑偡丅 堦墳丄愙懕偝傟偰偄傞I/O僨僶僀僗偵傛偭偰WAIT偺擖傝曽偑曄傢傞偺偐偲巚偄丄 弌椡愭億乕僩傪A0H偩偗偱偼側偔丄OUT (00H),A偲偟偰傒偨偺偱偡偑丄偙偺応崌傕摨條偺寢壥偱偟偨丅

懕偄偰OUT柦椷偺曄傢傝偵IN柦椷傪楢懕幚峴偟偰傒傑偡丅

IN柦椷偺応崌傕摨條偵丄+2Clock偲側傝傑偟偨丅

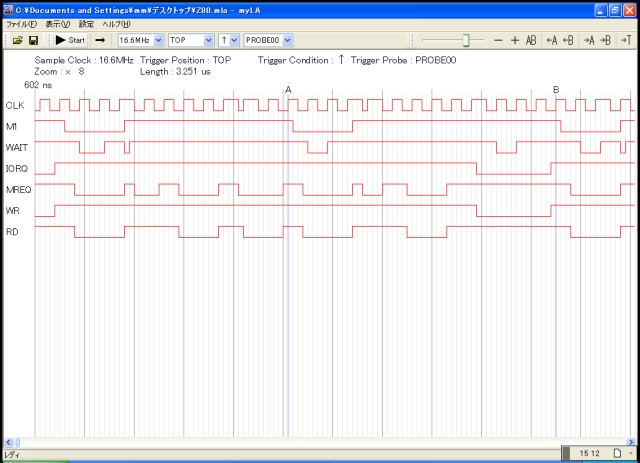

師偼OUT(C),r柦椷偱偡丅

OUT (C),r柦椷偼丄戞擇OP僐乕僪傪帩偪傑偡偐傜M1偑2夞懕偒傑偡丅偦傟偵壛偊偰IOREQ偺僞僀儈儞僌偱WAIT偑 擖傞偺偱慡晹偱15Clock偵側偭偰偄傑偡丅

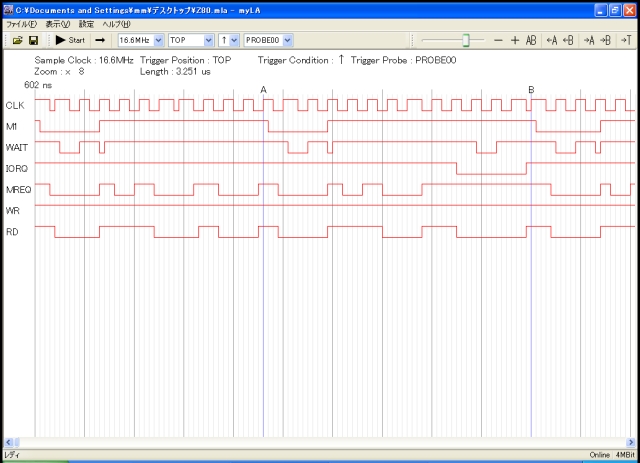

嵟屻偵丄儊儌儕儔僀僩柦椷偱偡丅

LD (nn),A柦椷傪儖乕僾幚峴偝偣傑偟偨偑丄WR怣崋敪惗帪偵WAI偼擖傝傑偣傫偱偟偨丅RD偲摨偠傛偆偱偡丅

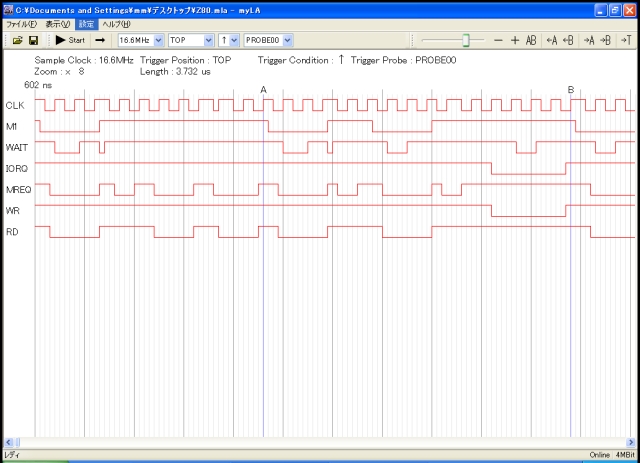

崱偺偲偙傠丄WAIT偑擖傞偺偼

偙傟傜偼RAM椞堟偱偺僾儘僌儔儉幚峴偺寢壥側偺偱丄ROM椞堟偱偼堘偆寢壥偵側傞壜擻惈偑偁傝傑偡丅

PC-6001MkII夝愅儅僯儏傾儖偵偼丄IO億乕僩偺F3H偱M1傗ROM椞堟丄RAM椞堟偺傾僋僙僗帪偵WAIT傪擖傟傞偐偳偆偐傪 愝掕曄峏偱偒傞傛偆側婰弎偑偁傝傑偡丅弶婜忬懺偼丄M1偲ROM傾僋僙僗偱WAIT偑擖傞傛偆偵側偭偰偄傑偡丅

幚嵺偵幚婡忋偱M1偱偺WAIT傪OFF偵偡傞傛偆愝掕偟丄儘僕傾僫偱挷傋偨偺偱偡偑丄 WAIT偼側偔側傝傑偣傫偱偟偨丅

ROM椞堟傾僋僙僗帪偺WAIT傪OFF偵偟丄BASIC偱扨弮側儖乕僾僾儘僌儔儉傪幚峴偟偨偲偙傠丄張棟懍搙偑岦忋偟傑偟偨丅 BASIC偺僀儞僞僾儕僞偑撪憼ROM偵偁傝丄偙偺椞堟傊偺傾僋僙僗懍搙偑岦忋偟偨偺偩偲巚傢傟傑偡丅 奜晹ROM丄偮傑傝ROM僇乕僩儕僢僕偵懳偟偰傕桳岠側偺偐偼挷傋偒傟傑偣傫偱偟偨丅

M1偲ROM椞堟椉曽偺WAIT傪OFF偵偡傞偲丄尒偨栚丄朶憱偟傑偡丅撪晹偱偳偺傛偆側朶憱忬懺偵偁傞偺偐傢偐傝傑偣傫偑丄 CRTC傪OFF偵偟偨屻偵M1/RAM偺WAIT傪OFF偵偡傞偲Z80帺懱偼傑偩摦偄偰偄傞傛偆側怣崋偺摦偒傪偟偰偄傑偟偨丅

IO億乕僩F3H偼丄MODE1偱傕桳岠側傛偆偱丄MODE1偱婲摦屻丄ROM椞堟偱偺WAIT傪OFF偵偡傞偲丄BASIC偺幚峴懍搙偑 岦忋偟傑偟偨丅

| 仭 [04/12/06] - SR怣崋慄 |

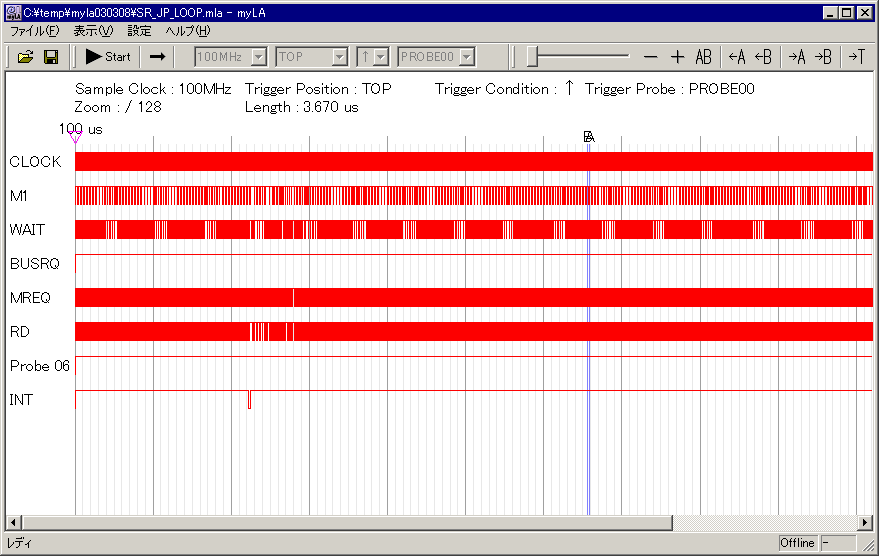

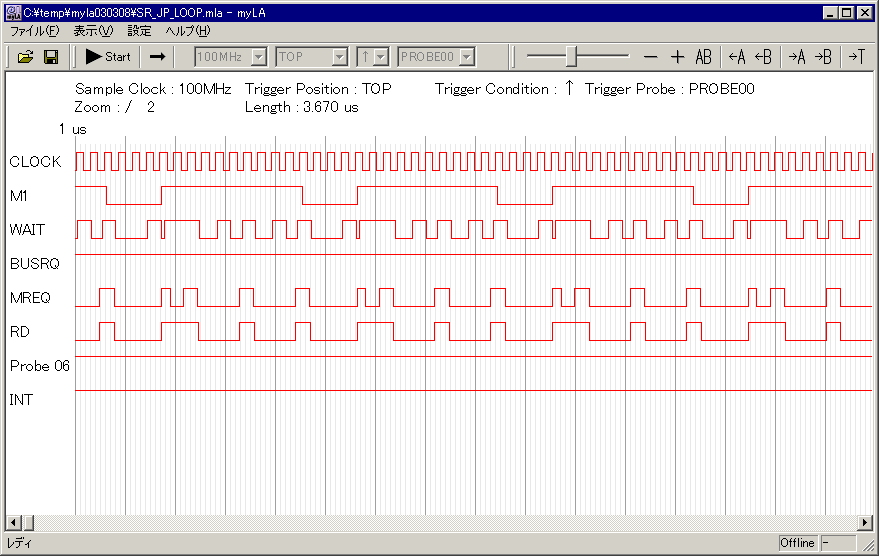

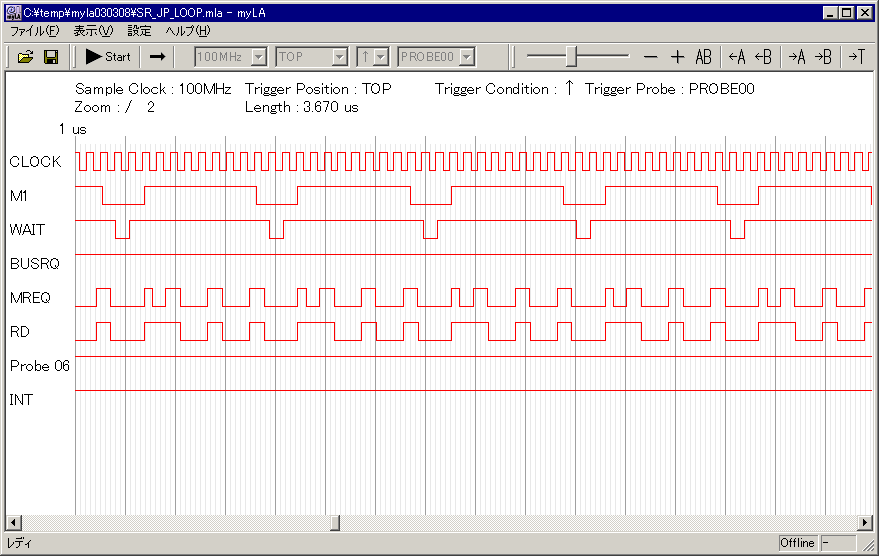

PC-6001MkIISR偺怣崋慄傪儘僕傾僫偱庢偭偰傒偨丅偙偺帪偺僾儘僌儔儉偼丄

C000: DI C001: JP C001H

偲偟偰丄扨弮偵RAM椞堟偺JP柦椷傪傂偨偡傜幚峴偡傞偲偄偆傕偺側偺偵丄 撪晹偱壗傪偟偰偄傞偺偐丄傑偭偨偔傢偐傜側偄丅WAIT怣崋偵偼慸偲枾側売強偑 偁傞偺偱丄偙傟偑悈暯昤夋偐壗偐偺僞僀儈儞僌側偺偐丅 WAIT怣崋傪惂屼偡傞偙偲偱丄Z80偲CRTC偑VRAM=MAIN RAM傊傾僋僙僗偡傞 僞僀儈儞僌傪偢傜偟偰偄傞傛偆偩丅2斣栚偺夋憸偑慸側売強偱丄3斣栚偺 夋憸偑枾側売強丅WAIT怣崋偑旕忢偵暋嶨丅 傕偟偐偡傞偲悅捈摨婜婜娫偱偼WAIT怣崋偺曄壔偑堘偆偺偐傕偟傟側偄丅 偦偺偁偨傝傕應掕偟偰偍偗偽傛偐偭偨丅

寢壥揑偵偼乽傛偔傢偐傜側偄乿偲偄偆偙偲偵側偭偰偟傑偭偨偑丄 棟桼偼暿偲偟偰丄偳傟偩偗偺WAIT偑偐偐偭偰偄傞偺偐偼撉傒庢傟傞偲巚偆丅

忋婰應掕偺枾偺売強偩偗偱側偔丄弶戙婡偱傕丄 WAIT怣崋偑擖偭偰偔傞偺偼M1僒僀僋儖帪偺傒丅 捠忢偺儊儌儕傾僋僙僗偵偍偄偰偼WAIT偼偐偐偭偰偄側偄帠偵拲堄丅

崱夞偼8049偵傕僾儘乕僽傪偁偰偨偺偩偑丄 8049偵愙懕偝傟偰偄傞偺偼CMT傗僉乕儃乕僪偲掅懍側廃曈I/O側偺偱丄 偆傑偔應掕偡傞偙偲偑偱偒側偐偭偨丅

應掕偟偨僨乕僞傪尒偨偄曽偼丄 MyLA傪棙梡偟偰偔偩偝偄丅MODE1偱偺寢壥傕擖偭偰偄傑偡丅偙偺僨乕僞傪棙梡偡傟偽丄WAIT偺暆傪兪昩扨埵偱 撉傒庢傞偙偲偑偱偒傑偡丅

| 仭 [02/11/09] - 壖憐僉乕儃乕僪 |

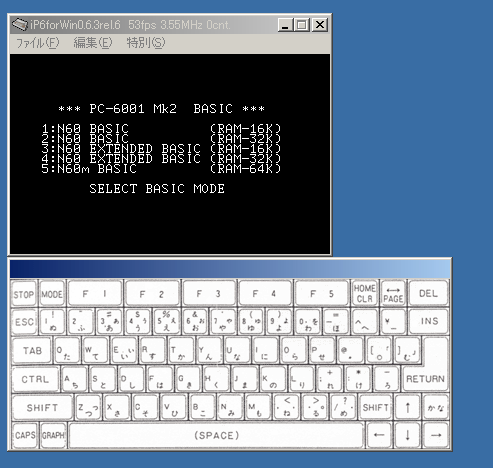

僆儂乕僣僋偲偐丄朸SF傾僪儀儞僠儍乕僎乕儉傪僨僶僢僌偟傛偆偵傕丄晛抜偼 101僉乕儃乕僪側偺偱丄僇僫偺埵抲偑傢偐傜側偄丅嵟弶偼幚婡偲尒斾傋側偑傜 傗偭偰偄偨偺偩偗傟偳旕忢偵嬯捝側偺偱僉乕攝抲恾傪PC-6001MkII偺儅僯儏傾儖偐傜 庢傝崬傫偱儅僂僗嵗昗傪庢摼偟偰...偲偄偆張棟傪壛偊偰傒偨條巕偑偙傟丅

乬傠乭偺僉乕傪墴偟偰傕弌側偄偺偼X斉偺僉乕張棟偑偦偆側偭偰偄偨偐傜偐側丅

SHIFT傗GRAPH僉乕偺張棟傪慻傒崬傫偱偄側偄偟丄GRAPH僉乕傪墴偟偨傜丄 傗偭傁傝壖憐僉乕儃乕僪偺攝抲恾傕曄傢傞偲偆傟偟偄偟丄JIS僉乕儃乕僪偼 姷傟偰偄側偄偺偱50壒攝抲儃僞儞偲偐傕梸偟偄側丄偲偐峫偊巒傔傞偲 旕忢偵庤娫偺偐偐傞偙偲偵側傝偦偆側偺偱曻抲拞丅偦偆偄偊偽X88000偼IME宱桼偱 擖椡偱偒傞偺偱偟偨偭偗丅

| 仭 [02/11/04] - 僆儂乕僣僋偵徚備 |

乽僆儂乕僣僋偵徚備乿偱僔乕儞4偐傜僔乕儞5傊偺儘乕僪偑弌棃側偄偲偄偆 儊乕儖偑撏偄偰偄偨偺偱挷傋偨偺偱偡偑丄尨場偼乬僥乕僾憱峴懍搙 > 儊僢僙乕僕昞帪懍搙乭 偲偄偆丄偄偮傕偺傗偮偱偟偨丅僀儊乕僕傪彂偒姺偊傞偲偄偆懳張偑偱偒側偄 宍幃側偺偱偍庤忋偘偱偡丅僄儈儏儗乕僞偱偺僥乕僾偺撉傒崬傒懍搙傪 棊偲偣偽偄偄偺偱偡偑丄撉傒崬傒帪娫偑幚婡暲偵側傝傑偡丒丒丒丅

僆儂乕僣僋偼傾僪儀儞僠儍乕僎乕儉偩偗偁偭偰僾儘僌儔儉偵 埫崋壔偭傐偄偙偲偑偝傟偰偄偰夝愅傕柺敀偐偭偨偱偡傛丄偼偄丅

| 仭 [02/09/8] - 僶僌庢傝 |

媣乆偵僄儈儏儗乕僞偺僐乕僨傿儞僌儈僗偵憳嬾偟傑偟偨丅

void SetTimerIntClock(long pow)

{

TimerInt_Clock = BaseTimerClock * ((pow + 1) / 4);

}

偲偄偆売強偑偁傝丄傢偞傢偞妵屖傪偮偗偰傑偱墘嶼惛搙傪壓偘偰傑偡偹丄愄偺儚僞僋僔丅 偙傟傑偱夝愅偟偰偒偨僜僼僩偱僞僀儅妱傝崬傒偺僞僀儈儞僌傪曄偊偰偄傞傕偺偼僪傾僪傾MkII偖傜偄偱丄 偙傟偼pow偺抣傪偲偰傕戝偒偔偟偰偄偨偺偱栤戣偑昞柺壔偟側偐偭偨偺偱偡偑丄愭擔丄 乽僟儊恖娫梴惉強mk2乿偝傫偺偲偙傠偺乽PSG壒尮僪儔僀僶 ver1.1乿偵懳墳偟偨嬋偱栤戣偑婲偒傞丄 偲K偝傫偵巜揈偝傟傑偟偰挷傋偨偲偙傠丄pow偵1偲偄偆抣偑擖偭偰偒偨帪偵墘嶼寢壥偑0偵側傞偲偄偆 僶僌偵婥偑晅偄偨傢偗偱偡丅

偮偄偱偵僥儔4001偑僨儌夋柺偐傜愭偵恑傑側偄偲偄偆僶僌傪挷傋傑偟偨丅 I/O億乕僩偺94H傪巊偭偰偄傞傛偆偱偟偰丄偙偺億乕僩偼90H偺塭偱偡偐傜丄CASE暥傪堦峴捛壛 偟偨傜愭偵恑傓傛偆偵側傝傑偟偨偲偝丅

| 仭 [02/09/4 .. part2] - Talk |

壒惡崌惉梡IC傊弌椡偝傟傞僨乕僞傪挱傔傛偆偲僼傽僀儖偵彂偒弌偟偟偰傒偨偺偩偗傟偳丄 偁傟丠廔抂暥帤楍偭偰0x00偑7屄偠傖側偐偭偨偭偗丠6屄偟偐弌椡偝傟偰偄側偄偺偱偡偗偳丄 偳偙偐偱姩堘偄偟偰傞偐僼傽僀儖弌椡偵僶僌偑偁傞丠

| 仭 [02/09/4] - BUSREQ Memo |

H LINE偺BUSREQ偼ON偑31.340兪s偱OFF偑22.350兪s丄V LINE偺BUSREQ偼ON偑4495.917兪s丅

| 仭 [02/09/3] - ROM僇乕僩儕僢僕 |

寢嬊丄Saver傪巊偭偰僐儞僶乕僩偟傑偟偨丅

幚婡傪堷偭挘傝弌偟偰偄傠偄傠丅儂儖儅儞僩偐偀丅 壒偺僪僐傑偱傪僄儈儏儗乕僩偟偨傜偄偄偺偐偭偰偄偭偨傜丄 AY3-8910偺弌椡抂巕偑僐儞僨儞僒偵愙懕偝傟偰偄偰僼傿儖僞偑丒丒丒 偲偄偆偲偙傠傑偱偐側丅幚婡偺曽偑壒偑傑傠傗偐(?)側偺偼丄偦偆偄偆傢偗偱偟偰丅

| 仭 [02/08/31] - ROM僇乕僩儕僢僕 |

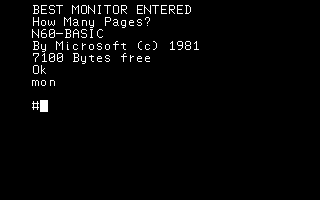

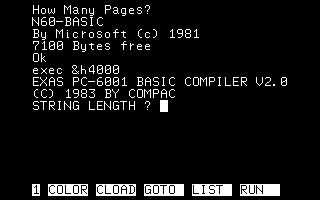

庤尦偵BASIC僐儞僷僀儔偲BEST儌僯僞偺ROM偑偁傞偺偱AKI80偱媧偄弌偦偆偲恀栭拞偺3帪偵僶僞僶僞偲 僙僢僥傿儞僌丅偱傕丄ROM儔僀僞晅懏偺FDD偑9801僼僅乕儅僢僩偱AT屳姺婡梡僜僼僩偑庢傝弌偣側偐偭偨傝丄 僔儕傾儖働乕僽儖偑25PIN偩偭偨傝丄嫇嬪偺壥偰偵ROM儔僀僞偑2732偵懳墳偟偰偄側偔偰巇愗傝側偍偟丅

BASIC僐儞僷僀儔偱専嶕偟偨傜丄偦偺嶌幰偝傫偺Web儁乕僕偑僸僢僩丅

杮嬈偑僎乕儉僔儑僂娭學偱僶僞僶僞偟偰偄偰戝曄側姶偠.

| 仭 [02/08/27] - 攇宍傪傒偨 |

弶戙婡傪暘夝偟偰攇宍傪傒偰傒傑偟偨丅傑偢偼M1偐傜丅 儊儌儕傾僋僙僗偵娭偟偰偼1Clock偺WAIT偑擖偭偰偄傑偡丅 偁丄ROM偲RAM偱堘偆偺偐偳偆偐挷傋朰傟傑偟偨丅Mk2埲崀偱偼堘偆偐傕偟傟傑偣傫丅

師偵BUSREQ偱偡丅BUSREQ偑嵶愗傟偵 曄壔偟偰偄傞売強偲丄HIGH偑楢懕揑偟偰偄傞晹暘偑傒偰偲傟傑偡丅 VIDEO僐儞僩儘乕儔偺HS/FS怣崋偵崌傢偣偰曄壔偟偰偄傑偡偹丅偱偡偺偱丄Z80偑摦嶌偱偒傞 偺偼丄悈暯婣慄婜娫偲悅捈婣慄婜娫偲偄偆偙偲偵側傝傑偡丅

懕偄偰INT偺敪惗僞僀儈儞僌丅TimerINT偺儔僀儞偑傢偐傜側偐偭偨偺偱 4040偺弌椡傪挷傋偰偄傑偡偑丄4040偺仾偵崌傢偣偰INT偑伀偑曄壔偟偰偄傑偡丅 偨偩丄偙偺帪偼BUSREQ偑ACTIVE側偺偱INT偼LOW偺傑傑偲側傝丄BUSREQ偑HIGH偵 側傞偲摨帪偵INT偑僋儕傾偝傟偰Z80偑妱傝崬傒傪庴偗擖傟偰偄傑偡丅側偺偱丄TimerINT偑敪惗偟偨帪偵 BUSREQ忬懺偱偁傟偽丄妱傝崬傒偼懸偨偝傟傞偙偲偵側傝傑偡丅僉儍僾僠儍夋柺偱偼僉乕儃乕僪傗 CMT妱傝崬傒偺敪惗尮偱偁傞8049偺儔僀儞曄壔偑弌偰偄傑偣傫偑丄 僞僀儅妱傝崬傒偲摨偠摦偒傪偟偰偄傑偟偨丅

偲偙傠偱僞僀儅妱傝崬傒偲8049宯偺妱傝崬傒偑摨帪偵敪惗偟偨応崌側偺偱偡偑丄 巆擮側偑傜挷傋傞偙偲偑偱偒傑偣傫偱偟偨丅忦審偑僔價傾偱偡偟丄偄偄僩儕僈僞僀儈儞僌偑側偄偺偱偡傛丅

| 仭 [02/08/24] - 攇宍傪傒偨偄 |

奺庬妱傝崬傒偑摨帪偵敪惗偟偨帪偭偰丄桪愭搙偺掅偄妱傝崬傒偼懸偨偝傟傞偺偱偟傚偆偐丄 偦傟偲傕僉儍儞僙儖偝傟偰偟傑偆偺偱偟傚偆偐丅

悈暯昤夋帪偲悅捈昤夋帪偵偼BUSREQ偑敪峴偝傟傞偺偱Z80偼巭傑傞偙偲偵側偭偰偄傞偺偱偡偑丄 悈暯昤夋帪偺婣慄婜娫傕巭傑偭偰偄傞偺偱偟傚偆偐丅傑偨丄昤夋OFF儌乕僪偱偼BUSREQ偑 敪峴偝傟傑偣傫偑丄昤夋ON偵偟偨帪偼丄偳偺僞僀儈儞僌偱昤夋偑巒傑傞偺偱偟傚偆偐丠搑拞偐傜丠 偦傟偲傕悅捈婣慄廔椆屻偐傜丠

偲偐傑偀丄嵶偐偄媈栤偑偄偔偮偐偁傝傑偟偰丄夞楬恾傪傒偰傕傛偔傢偐傜側偄偺偱偡偹丅 偦偆偄偆帪偵偼傑傛傢偢攇宍傪傒傟偽偄偄偲偄偆偙偲偱丄拲暥偟傑偟偨傛丄 僆僾僥傿儅僀僘偝傫偺僇儊儗僆儞USB+儘僕傾僫丅 儘僕傾僫僜僼僩偼丄Psxpad偝傫偺偲偙傠偺偐傜丅 摦嶌妋擣偼廔傢偭偨偺偱丄柧擔偵偱傕PC-6001傪僶儔偟偰攇宍傪傒偰傒傛偆偲巚偄傑偡丄妝偟傒丅

| 仭 [02/08/22] - BUSREQ |

嵟嬤偢偭偲僿僢僪僼僅儞偮偗偰PSG側壒傪挳偄偰偄偨偐傜帹偑捝偄丅

幚婡偱僴僀僪儔僀僪傪婲摦偟偰傒傞偲丄慡慠懍搙偑堘偆乣丅僗僥僢僾悢寁嶼傪娫堘偊偨偐側偀偲 挷傋偰傒偰傕栤戣側偄丅昤夋WAIT傪0偵偟偨偔傜偄偱偪傚偆偳偄偄側丒丒丒偭偰丄傑偝偐丄 CRT OFF傪巊偭偰偄傞偺偱偼両丠偲巚偭偨傜戝摉偨傝丅崅懍昤夋偡傞側傜儃僋傕摨偠曽朄傪巊偭偨偩傠偆偗偳丄 RF儌僕儏儗乕僞偱TV偵偮側偄偱偄傞帪偵偼嵒棐偑昞帵偝傟傞壜擻惈偑偁傞偐傜嬛偠庤偩偲巚偭偰偄傑偟偨丅 偨偩丄抁帪娫偱偁傟偽栤戣側偔丄僴僀僪儔僀僪偱偼LDI偲EX偲LD HL,SP偺慻傒崌傢偣傪巊偭偨傝偟偰丄 偦偺曈偼峫偊傜傟偰偄傞側偀偲丅偁傝傖丄DoorDoorMk2偱傕僞僀僩儖夋柺偱慡夋柺僋儕傾帪偵巊梡偟偰傞側丅

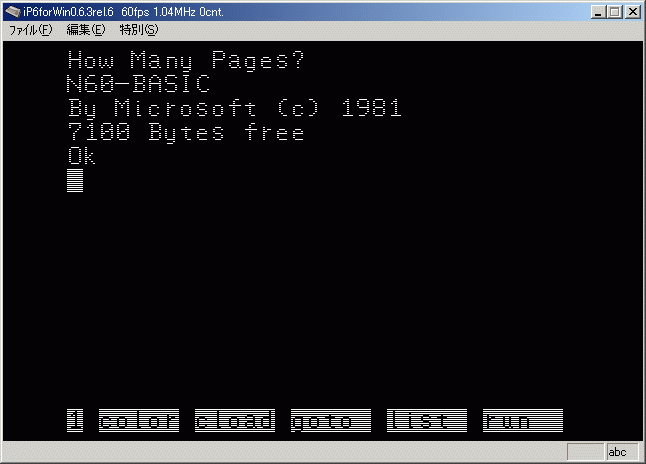

| 仭 [02/08/19] - version0.64 rel6 |

僄儈儏儗乕僞偺廔椆帪偵棊偪傞乮廔椆偡傞偱偼側偔乯偲偄偆曬崘偑偁傞偺偱偡偑丄 庤尦偺娐嫬偱嵞尰偣偢崲傝拞丅

僄儞儀儘乕僾偑抁偄偲偄偆偛巜揈偑偁傝傑偟偨傛偆偵壒偵懳偟偰柍撢拝偡偓偱偟偨丅 彮偟偩偗庤傪壛偊偨偩偗偱Chack'nPop偺壒偑柭傝弌偟傑偟偨丄側傞傎偳丅偦傟偱傕傑偩傑偩偱偡偗偳丅 堦擔拞丄1KHz偺嬮宍攇傪挳偄偰偄偨偺偱帹偑偍偐偟側姶偠丅

| 仭 [02/08/17] - version0.64 rel6 |

晄搒崌偑偨偔偝傫弌傞偐偲巚傢傟傑偡丅僗僥乕僞僗僶乕偼柍偔偡曽岦偱峫偊偰偄傑偡丅偙偺庤偺 摦嶌忣曬偼暿僂傿儞僪僂偵傑偲傔偰弌偦偆偲巚偄傑偟偰丅

壒偵僲僀僘偑偨偭傉傝丒丒丒丅

| 仭 [02/06/29] - sound |

僒僂儞僪僪儔僀僶廃傝傪廋惓拞丅30暘傎偳1KHz偺僥僗僩傪偟偰偄偨偺偱帹偑僿儞偵側傝偦偆丅

| 仭 [02/06/25] - Virtual66SR |

PC-6601SR僄儈儏儗乕僞偺Virtual66SR偲偄偆偺偑偁傞偦偆偱偡丄偡偽傜偟偄丅

| 仭 [02/06/16] - SR偺VRAM 偦偺4 |

VRAM傪偁傟偙傟偲彂偒姺偊偰傒偨偙偲傪MEMO偟偰偍偒傑偡丅PRE僞僌巊偭偰傞傫偱 昞帵偑僌僞僌僞偐傕丅

-SCREEN2- REM (256,0)偑VRAM偺0000H偵懳墳偟偰偄傞傜偟偄 PSET(256,0),16 0000: 0F 00 00 00 00 00 00 00 0008: 00 00 00 00 00 00 00 00 REM 1僶僀僩偱2Pixel傜偟偄 PSET(256,0),16 0000: FF 00 00 00 00 00 00 00 PSET(257,0),16 0008: 0F 00 00 00 00 00 00 00 REM 2僶僀僩偱4Pixel偼椬傝崌偭偰偄傞偗偳... PSET(256,0),16 0000: 0F 0F 00 00 00 00 00 00 PSET(258,0),16 0008: 00 00 00 00 00 00 00 00 REM 2僶僀僩扨埵偱旘傃旘傃傜偟偄 FOR I=0 TO 15 0000: 10 32 00 00 54 76 00 00 PSET(256+I,0),I+1 0008: 98 BA 00 00 DC FE 00 00 NEXT REM 嬼悢儔僀儞偲婏悢儔僀儞偑岎屳偵側傜傫偱偄傞傜偟偄 FOR I=0 TO 15 0000: 00 00 12 32 00 00 54 76 PSET(256+I,1),I+1 0008: 00 00 98 BA 00 00 DC FE NEXT REM Y=2偼0100H偐傜巒傑傞傜偟偄 FOR I=0 TO 15 0100: 10 32 00 00 54 76 00 00 PSET(256+I,2),I+1 0108: 98 BA 00 00 DC FE 00 00 NEXT REM Y=4偼0040H偐傜巒傑傞傜偟偄...偪傚偭偲曄懃揑丠 FOR I=0 TO 15 0040: 10 32 00 00 54 76 00 00 PSET(256+I,4),I+1 0048: 98 BA 00 00 DC FE 00 00 NEXT REM 埲壓丄摨條偵挷傋偰傒傞偲...婯懃惈偼偁傞偗偳偹偉 PSET(256+I,6),I+1 0140: PSET(256+I,8),I+1 0080: PSET(256+I,10),I+1 0180: PSET(256+I,12),I+1 00C0: PSET(256+I,14),I+1 01C0: PSET(256+I,16),I+1 0200: PSET(256+I,18),I+1 0300: PSET(256+I,20),I+1 0340: REM (0,0)偼1A00H偐傜巒傑傞傜偟偄 PSET(I,0),I+1 1A00: 10 32 00 00 54 76 00 00 REM 埲壓丄摨條偵挷傋偰傒傞偲丄偙偪傜偼慺捈側暲傃 PSET(I,2),I+1 1B00: 10 32 00 00 54 76 00 00 PSET(I,4),I+1 1C00: 10 32 00 00 54 76 00 00 PSET(I,6),I+1 1D00: 10 32 00 00 54 76 00 00 PSET(I,8),I+1 1E00: 10 32 00 00 54 76 00 00 PSET(I,10),I+1 1F00: 10 32 00 00 54 76 00 00 PSET(I,12),I+1 2000: 10 32 00 00 54 76 00 00 PSET(I,14),I+1 2100: 10 32 00 00 54 76 00 00 PSET(I,16),I+1 2200: 10 32 00 00 54 76 00 00 -SCREEN3- REM (512,0)偑VRAM偺0000H偵側傞傜偟偄 PSET(512,0),4 0000: 80 80 00 00 00 00 00 00 REM 嬼悢儔僀儞偲婏悢儔僀儞偑岎屳偵暲傫偱偄傞傜偟偄 PSET(512,1),4 0000: 00 00 80 80 00 00 00 00 REM 2僶僀僩偱8Pixel傜偟偄 LINE(512,0)-(519,0),4 0000: FF FF 00 00 00 00 00 00 REM SCREEN2偲堘偭偰慺捈偵暲傫偱偄傞丠 PSET(512,0),4 0000: 80 80 00 00 80 80 00 00 PSET(520,0),4 0008: 80 80 00 00 80 80 00 00 PSET(528,0),4 PSET(536,0),4 REM 慺捈偱傛偄 LINE(512,0)-(639,0),4 0000: FF FF 00 00 FF FF 00 00 00xx: 棯 0038: FF FF 00 00 FF FF 00 00 0040: 00 00 00 00 00 00 00 00 REM (0,0)偑VRAM偺1A00H偵側傞傜偟偄 PSET(0,0),4 1A00: 80 80 00 00 00 00 00 00

側傫偲側偔尒偊偰偒傑偟偨丅

Macintosh G4 Cube傪忳偭偰傕傜偄丄帺戭偵帩偭偰婣傝傑偟偨丅 OS-X偱偁傟偙傟傗偭偰傒偨偄偲偙傠偱偡偗偳丄Objective-C偩偗側傜偲傕偐偔丄 偁偺僼儗乕儉儚乕僋傑偱棟夝偟側偄偲偄偗側偄偺偼柺搢偩側偀偲丅 Windows偱傕MFC側傫偐傕巊傢偢偵Win32SDK偩偗偱傗偭偰傞儚僞僋僔偲偟偰偼丄 Mac偱傕C尵岅偲API偩偗偺娐嫬偑梸偟偄偺偱偡偑丅

| 仭 [02/06/12] - SR偺VRAM 偦偺3 |

撉傒崬傒儊儌儕偺Bank愗傝懼偊(I/O偺60h乣67h)偵偍偄偰傕16K偺暻偑偁傞傛偆偱偡丅

CPU嬻娫偺8000h偵RAM偺0000h傪妱傝摉偰傞 ... OK CPU嬻娫偺8000h偵RAM偺2000h傪妱傝摉偰傞 ... RAM偺0000h偑弌偰偔傞 CPU嬻娫偺8000h偵RAM偺4000h傪妱傝摉偰傞 ... OK CPU嬻娫偺A000h偵RAM偺0000h傪妱傝摉偰傞 ... RAM偺2000h偑弌偰偔傞 CPU嬻娫偺A000h偵RAM偺2000h傪妱傝摉偰傞 ... OK CPU嬻娫偺A000h偵RAM偺4000h傪妱傝摉偰傞 ... RAM偺6000h偑弌偰偔傞慜敿偼慜敿丄屻敿偼屻敿偵偟偐妱傝摉偰傜傟側偄傛偆偱偡偹丅

傕偆1偮師偺庤弴偱儊儌儕傪愗傝懼偊偰丄

(1)CPU嬻娫偺8000h偵RAM偺0000h傪妱傝摉偰傞 ... OK (2)CPU嬻娫偺A000h偵RAM偺4000h傪妱傝摉偰傞 ... RAM偺6000h偑弌偰偔傞偙偺傛偆偵偟偰傕(2)偺塭嬁偱(1)偺妱傝摉偰傾僪儗僗偑0000h偵側偭偰 偟傑偆傛偆側偙偲偼偁傝傑偣傫偱偟偨丅

SCREEN1偱偼ASCII僐乕僪偲傾僩儕價儏乕僩偑岎屳偵暲傫偱偄傞扨弮側VRAM峔惉偱偡丅

SCREEN3偺応崌...

screen 3,2,2 line(0,0)-(639,0),4 偱偼丄 0000: FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 0010: FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 0020: FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 0030: FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 0040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0050: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 偙偆側傝傑偡丅 screen 3,2,2 line(0,1)-(639,1),4 偱偼丄 0000: 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 0010: 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 0020: 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 0030: 00 00 FF FF 00 00 FF FF 00 00 FF FF 00 00 FF FF 0040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0050: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 偙偆側傝傑偡丅

儅僯儏傾儖忋偱偼4僶僀僩偱8Pixel(4怓側偺偱RGB奺2bit)偲彂偐傟偰偄傞偺偱偡偑丄 Z80傪捠偟偰VRAM偵傾僋僙僗偡傞偲4bit偑2僶僀僩偵僷僢僋 偝傟偨忬懺偲側傝傑偡丅

傑偨丄婏悢儔僀儞偲嬼悢儔僀儞偑岎屳偵弌偰偒偰偄傞偺偑傢偐傝傑偡丅

SCREEN2偺応崌...

screen 2,2,2 CLS line(0,0)-(319,0),4 偱偼丄 0000: 44 44 00 00 44 44 00 00 44 44 00 00 44 44 00 00 0010: 44 44 00 00 44 44 00 00 44 44 00 00 44 44 00 00 0020: 44 44 00 00 44 44 00 00 44 44 00 00 44 44 00 00 0030: 44 44 00 00 44 44 00 00 44 44 00 00 44 44 00 00 0040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0050: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 偙偆側傝傑偡丅 screen 3,2,2 CLS line(0,1)-(319,1),5 偱偼丄 0000: 00 00 55 55 00 00 55 55 00 00 55 55 00 00 55 55 0010: 00 00 55 55 00 00 55 55 00 00 55 55 00 00 55 55 0020: 00 00 55 55 00 00 55 55 00 00 55 55 00 00 55 55 0030: 00 00 55 55 00 00 55 55 00 00 55 55 00 00 55 55 0040: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 0050: 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 偙偆側傝傑偡丅

儅僯儏傾儖忋偱偼1Pixel偱1僶僀僩偲彂偐傟偰偄傞偺偱偡偑丄 Z80傪捠偟偰VRAM偵傾僋僙僗偡傞偲4bit偑2僶僀僩偵僷僢僋偝傟偨忬懺偲側傝傑偡丅 2僶僀僩偱2Pixel偱偡丅

傑偨丄婏悢儔僀儞偲嬼悢儔僀儞偑岎屳偵弌偰偒偰偄傞偺偑傢偐傝傑偡丅

偨偩丄I/O億乕僩偵Y嵗昗傪巜帵偡傞 堊偺儗僕僗僞偑偁傝丄偙傟偵傛偭偰儊儌儕僐儞僩儘乕儔偑僨乕僞偺暲傃傪擖傟懼偊偰偄傞 偱偟傚偆偐傜丄偙傟傜偺寢壥傪塋撣傒偵偡傞偙偲偼偱偒傑偣傫丅

偝傜偵柺搢側偺偼VRAM忋偱偺僨乕僞偺暲傃偲攝抲偱偟偰丄偦傟偼柧擔埲崀偵懕偔丄偲丅

| 仭 [02/06/11] - SR偺VRAM 偦偺2 |

VRAM偐傜偺儕乕僪偼MAIN RAM偺0000h傪CPU嬻娫偺8000h偵忋偘偰丄X嵗昗傪HL偵擖傟偰嵟忋埵Bit傪ON偵偟偰 偐傜LD偡傞丅僫僯儐僄0000斣抧丠MAIN RAM偼32K丄VRAM偑32K偁傞傛偆側姶偠側傫偩偗偳丄 幚嵺偵偳偆偐偼偲傕偐偔丄僄儈儏儗乕僞偱偦偆偄偆晽偵幚憰偟偰傕傛偝偦偆丅

偄傑偩偵MAIN RAM偺峔惉傕棟夝偑懌傝側偐偭偨傝偡傞丅32KBytes偟偐側偄傛偆偵尒偊傞傫偩偗偳丅

弶怱偵栠偭偰PC-6001mkIISR偺庢埖愢柧彂傪奐偔丅 僽儘僢僋僟僀傾僌儔儉偺僶僗傪尒傞偲...儊儌儕僐儞僩儘乕儔偑DRAM偵偮側偑偭偰側偄偟両側偵偦傟丅 偭偰偄偆偐丄Z80偲DRAM偺僨乕僞僶僗偑偮側偑偭偰側偄偟両

DRAM傪惂屼偟偰偄傞偺偼CRT僐儞僩儘乕儔2偺傒偱丄D-RAM偺僶僗偼摨偠偔CRT僐儞僩儘乕儔2偲VRAM僨乕僞僶僗 偑丄CRT僐儞僩儘乕儔1偲VRAM傾僪儗僗僶僗偑愙懕偝傟偰偄傞傜偟偄丅偁丄VRAM偲偼DRAM偱偁偭偰丄儊僀儞偺 RAM偺偙偲偱偡偹丅儊儌儕僐儞僩儘乕儔偼奺庬ROM偲Z80偲愙懕偝傟偰偄傞偲丅偝傜偵偝傜偵丄Z80僨乕僞僶僗偼 CRT僐儞僩儘乕儔2偲愙懕偝傟偰丄Z80傾僪儗僗僶僗偼CRT僐儞僩儘乕儔1偲愙懕偝傟偰偄傞丅 儊儌儕僐儞僩儘乕儔偲CRT僐儞僩儘乕儔偺偮側偑傝偼側偄丅Z80偼CRT僐儞僩儘乕儔傪宱桼偟側偄偲 儊儌儕偵傾僋僙僗偱偒側偄偭偰偙偲偱偡偐丠

P6偵偼僛儞僛儞娭學側偄偗偳丄屵屻偺崙GREACE SIDE偑嵞奐偟偰偨丅

| 仭 [02/06/10] - SR偺VRAM |

VRAM偼僼儔僢僩側儊儌儕峔惉偩偲巚偄崬傫偱偄偨傜慡慠堘偆偟丅W巵偺帒椏傪撉傫偱偐傜丄

PSET/POINT柦椷偺媡傾僙儞僽儖儕僗僩傪撉傫偩傝丅640x200偺帪偼4Bytes偱8Pixel偱

160Bytes/Line偲偄偆峔惉傜偟偔妱偲扨弮丅栤戣偼320x200偺帪偱丄傢偗偑傢偐傜傫丅

VRTC偲RAM傪偳偆傗偭偰愙懕偟偰偄傞傫偩偐丅儊儌儕傾僋僙僗儖乕僠儞偼

Z80Core偱昿斏偵屇傃弌偝傟傞偐傜丄偙偙偵忦審暘婒傪彂偒壛偊偨偔偼側偄偺偩偗傟偳丅

[掶惓]320x200偩偲僼儔僢僩傜偟偄丅丒丒丒傑偰傑偰丄320x200偱偼1Pixel偱1Byte偩偐傜

64000Bytes昁梫偩偗偳丄SR偺巇條偼2夋柺庢傟傞偲丅VRAM偼128Kbytes愊傫偱傞丠傢偗側偔偰丄

1Pixel偱1Bytes偺忋埵4Bit偼巊偭偰偄側偙偲偐傜丄VRAM偺峔憿乮偲偄偆偐CRTC偐傜偺傾僋僙僗乯偼

傾僪儗僗僶僗8杮扨埵偱暘偐傟偰偄傞偲峫偊傜傟傞偲丅偱傕丄W巵偺夝愅偲堘偭偰偒偪傖偆偟丄

X斉偱偼幚嵺偵摦嶌偟偰偄傞偺偩偐傜丄偳偙偐偟傜儃僋偑姩堘偄傪偟偰偄傞偭傐偄丅

I/O億乕僩偵棳傟傞僨乕僞傪傒偰偄偰傕傢偐傞傛偆偵丄偲偵偐偔VRAM傊偺傾僋僙僗偑 暋嶨偱廳偡偓丅SR偭偰巊偄偵偔偄丅僎乕儉僜僼僩偑弌側偐偭偨偺偼帪戙偺棳傟偩偗偱側偔偰 傾乕僉僥僋僠儍偵傕栤戣偑偁偭偨偺偩側偀偲巚偭偨傝丅

| 仭 [02/06/09] - SR偺RAM |

RAM傊偺傾僋僙僗偼16Kbytes扨埵偱8Kbytes偟偐慖戰偱偒側偄丠丒丒丒傛偔傢偐傜傫偱偡丄偼偄丅 偮傑傝屻傠敿暘偺8KBytes偼偮偐偊側偄偭偰僐僩丠

ROM偺撉傒崬傒丄儊儌儕儅僢僾偲娭學偡傞I/O億乕僩丄悅捈摨婜妱傝崬傒儌僪僉傪 偔偭偮偗偨傜丄VRAM傪彂偒姺偊巒傔偨丅棃廡偼昤夋張棟偲偄偆偙偲偱丅 丒丒丒VRAM攋夡偟偰傞偩偗偩偭偨傜媰偗傞丅

| 仭 [02/06/04] - 夋柺僒僀僘 |

SR偼廲曽岦偵204Line偁傞偲偄偆偙偲傪偡偭偐傝朰傟偰傑偟偨丅偙偆側傞偲僂傿儞僪僂傪 640x480偵偟偰僙乕僼僥傿傪娷傔偨柍昤夋晹暘傕梡堄偟偰傗傠偆偐偲偄偆婥偵傕側偭偨傝偟傑偡偗偳丅

| 仭 [02/06/01] - 儕儞僋 |

曻抲偟偰偄傞娫偵傕奺曽柺偺曽乆偐傜儊乕儖傪捀偄偰偄傑偟偰丄PC-6001宯 偺僒僀僩傪棫偪忋偘傜傟偨曽傕偄傜偭偟傖偄傑偟偨偐傜丄偙偙偱偮側偄偱偍偒傑偡丅僐僐偺TOP偵偁傞儕儞僋廤傪埨堈偵彂偒姺偊偲WWWC/WWWD偑斀墳 偟偰偟傑偄丄亀僄儈儏儗乕僞杮懱偑峏怴偝傟偨丠両亁偲巚傢偣偰偟傑偆偺傕 怽偟栿側偄偺偱丅

傕傟偑偁偭偨傜怽偟栿偁傝傑偣傫丅

MODE1偺screen3/4偑弌傞傛偆偵側偭偰EGGY偲偐僗儁僴儕偲偐TINY XEVIOUS偁偨傝偑 640x400偱昞帵偱偒傞傛偆偵側偭偨丅AX-7偁偨傝偼傑偭偨偔僟儊側傫偩偗偳丄昤夋張棟偑 棟夝偱偒偰偄側偄偺偲丄摦嶌妋擣梡偺僾儘僌儔儉偑側偄偺偱曻抲丅

| 仭 [02/05/31] - 2攞 |

1儢寧偵堦帪娫偖傜偄偺儁乕僗偱僐乕僪彂偒姺偊偰傑偡偐傜丄僇僞僠偵 側傞傕偺偑弌棃忋偑傞傑偱偵偼丄偐側傝偺帪娫傪梫偡傞傢偗偱偟偰丅偦傟偱傕 SR懳墳偺弨旛偲偟偰640x200偱偺昤夋偐傜丅BASIC偱偺奺SCREEN儌乕僪偼妱偲僇儞僞儞側傫偱偡偑丄MC6847偑帩偭偰偄傞懠偺儌乕僪偱偺昤夋張棟偑僒僢僷儕傢偐傝傑偣傫丅

偦偺偆偪丄isio偝傫偵嫵偊傪岊偆偲偄偆偙偲偱丒丒丒丅